# 70V, 2.5mA Precision Protection APD Bias Dual-Gain Track/Hold Current Mirror

#### GENERAL DESCRIPTION

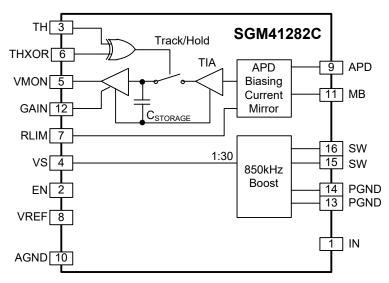

The SGM41282C integrates a Boost converter for generating up to 70V regulated output, a 1×/8× dual-gain current mirror with a track and hold output buffer, which is unique to simplify the fiber module circuit design due to the use of low resolution ADC.

The SGM41282C is available in a Green TQFN-3×3-16L package.

#### **APPLICATIONS**

Fiber Modules with APD Photon Sensor Laser Beam Finders (LIDA)

#### **FEATURES**

- Input Voltage Range: 2.8V to 5.5V

- Wide Output Voltage Range from (V<sub>IN</sub> + 5V) to 70V

- 850kHz Switching Frequency

- 1:30 Output Voltage Programming

- Adjustable Over-Current Protection

- Internal 1×/8× Dual-Gain Current Mirror

- 2.5V Voltage Buffer for Full-Scale Output Current

- Less than 1µA Shutdown Current

- Full Chain Circuit: Bias-Mirror-Track/Hold

- Replacement of \*15059/\*3430+\*3923

- Available in a Green TQFN-3×3-16L Package

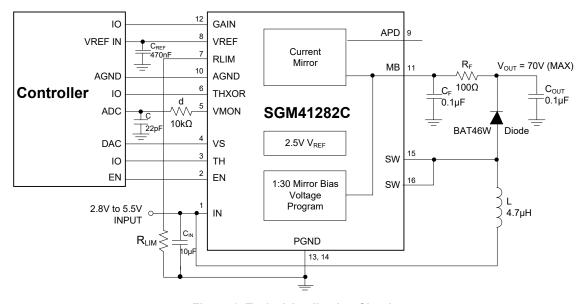

#### TYPICAL APPLICATION

Figure 1. Typical Application Circuit

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM41282C | TQFN-3×3-16L           | -40°C to +85°C                    | SGM41282CYTQ16G/TR | MNETQ<br>XXXXX     | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, EN, VS, TH, THXOR, VMON, RLIM   | , VREF, GAIN                 |

|-------------------------------------|------------------------------|

|                                     | 0.3V to 6V                   |

| SW, MB                              |                              |

| APD                                 | $-0.3V$ to $(V_{MB} + 0.3V)$ |

| Package Thermal Resistance          |                              |

| TQFN-3×3-16L, θ <sub>JA</sub>       | 41.7°C/W                     |

| TQFN-3×3-16L, θ <sub>JB</sub>       | 16.2°C/W                     |

| TQFN-3×3-16L, $\theta_{JC (TOP)}$   | 46.6°C/W                     |

| TQFN-3×3-16L, θ <sub>JC (BOT)</sub> | 4.5°C/W                      |

| Junction Temperature                | +150°C                       |

| Storage Temperature Range           | 65°C to +150°C               |

| Lead Temperature (Soldering, 10s)   | +260°C                       |

| ESD Susceptibility                  |                              |

| HBM                                 | 2000V                        |

| CDM                                 | 1000V                        |

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range                 | 2.8V to 5.5V   |

|--------------------------------------|----------------|

| V <sub>APD</sub> Range               | 20V to 70V     |

| I <sub>APD</sub>                     | <2mA           |

| Operating Ambient Temperature Range  | 40°C to +85°C  |

| Operating Junction Temperature Range | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

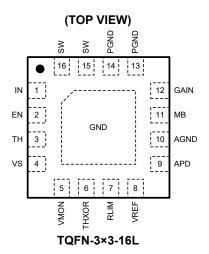

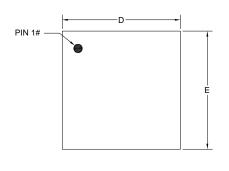

### **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN            | NAME  | TYPE (1) | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | IN    | Р        | Power Input to All Internal Circuits. Bypass IN to PGND with a ceramic capacitor of 10μF minimum value.                                                                                                                                                                                                                                                                                                                                             |

| 2              | EN    | I        | Enable Input. Input high to enable this chip, and low to shut down the chip.                                                                                                                                                                                                                                                                                                                                                                        |

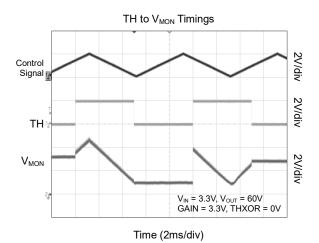

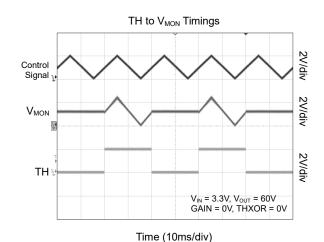

| 3              | ТН    | I        | Track or Hold Input. Input high for tracking (when THXOR is logic low, check THXOR description for more detail), where the VMON follows the current output of the APD pin simultaneously. Input low for holding where the VMON outputs a snapshot of APD current captured right after the following edge of the signal applied on the TH pin, in which the APD current snapshot is converted into a voltage and is stored in an internal capacitor. |

| 4              | VS    | I        | Proportional input for programming the MB voltage with an increment gain of 1:30.                                                                                                                                                                                                                                                                                                                                                                   |

| 5              | VMON  | 0        | Current Monitoring Output. Its voltage is proportional to the current of the APD pin.                                                                                                                                                                                                                                                                                                                                                               |

| 6              | THXOR | I        | Logic Input. Effective logic level for selecting the tracking state at the TH input. The complementary logic level to the logic level of the THXOR at the TH is put for tracking.                                                                                                                                                                                                                                                                   |

| 7              | RLIM  | I        | Current Limit Program Pin. Use an external resistor to set current limit threshold. Connect a resistor from this pin to signal ground.                                                                                                                                                                                                                                                                                                              |

| 8              | VREF  | 0        | Reference Voltage Output.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9              | APD   | 0        | Output for Biasing the APD Device. The current out of this pin is sampled with a mirror circuit for current monitoring and over-current protection.                                                                                                                                                                                                                                                                                                 |

| 10             | AGND  | G        | Signal Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11             | MB    | I        | Mirror Bias Input. Connect to the Boost stage output. Do not leave it floating.                                                                                                                                                                                                                                                                                                                                                                     |

| 12             | GAIN  | I        | $1\times/8\times$ Gain Selection Input. Input low to select $1\times$ gain and high to select $8\times$ gain, where the $1\times$ gain has an equivalent conversion gain of $1.25k\Omega$ and $10k\Omega$ for $8\times$ gain.                                                                                                                                                                                                                       |

| 13, 14         | PGND  | G        | Power Ground. Returns of the $C_{\text{IN}}$ and $C_{\text{OUT}}$ capacitors should be connected close to this pin. Connect to system ground, exposed pad and AGND together.                                                                                                                                                                                                                                                                        |

| 15, 16         | SW    | 0        | Low End Boost Switch Output. Inductor should be connected between $C_{\text{IN}}$ capacitor and this pin, Diode should be connected between this pin and $C_{\text{OUT}}$ capacitor. Put inductor and diode as close to this pin as possible to minimize parasitic impedance and thermal resistance.                                                                                                                                                |

| Exposed<br>Pad | GND   | G        | Exposed Pad. It is on the bottom side of device and not actually electrically connected to any electrical net. Connect the exposed pad to AGND and PGND using a large copper plane during PCB layout for better thermal performance.                                                                                                                                                                                                                |

NOTE: I: input, O: output, G: ground, P: power for the circuit.

## **ELECTRICAL CHARACTERISTICS**

( $V_{IN} = 3.3V$ . Full = -40°C to +85°C, typical values are at  $T_J = +25$ °C, unless otherwise noted.)

| PARAMETERS                             | SYMBOL                | CONDITIONS                                                                         | TEMP  | MIN  | TYP  | MAX   | UNITS  |

|----------------------------------------|-----------------------|------------------------------------------------------------------------------------|-------|------|------|-------|--------|

| Supply Voltage Range                   | V <sub>IN</sub>       |                                                                                    | Full  | 2.8  |      | 5.5   | V      |

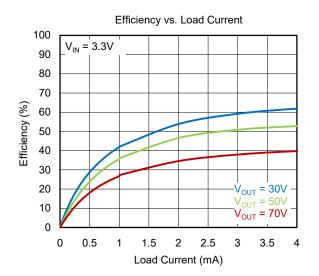

| Efficiency                             | η                     | 70V, 1mA loading                                                                   | +25°C |      | 26   |       | %      |

| Quiescent Current                      | IQ                    |                                                                                    | Full  |      | 1.3  | 2     | mA     |

| Under-Voltage Lockout Threshold        | V <sub>UVLO</sub>     | V <sub>IN</sub> rising                                                             | Full  | 2.4  | 2.5  | 2.6   | V      |

| Under-Voltage Lockout Hysteresis       | V <sub>UVLO_HYS</sub> |                                                                                    | +25°C |      | 200  |       | mV     |

| Shutdown Current                       | I <sub>SHDN</sub>     | V <sub>SHDN</sub> = 0V                                                             | Full  |      | 0.01 | 1     | μΑ     |

| Output Short Circuit Operation Current | I <sub>SHRT</sub>     | $V_{OUT} = 40V$ , $R_{LIM} = 28k\Omega$                                            | +25°C |      | 80   |       | mA     |

| BOOST and APD Biasing                  |                       |                                                                                    |       |      |      |       |        |

| Switching Frequency                    | f <sub>SW</sub>       |                                                                                    | Full  | 750  | 850  | 950   | kHz    |

| Maximum Duty Cycle                     | D <sub>MAX</sub>      |                                                                                    | Full  | 86.5 | 90   | 92    | %      |

| $V_{VS}$ to $V_{MB}$ Programming Ratio | VPR                   |                                                                                    | Full  | 29   | 30   | 31    | V/V    |

| Boost Start-Up Time                    | t <sub>UP</sub>       | From EN to 90%, 70V output voltage, 1mA load                                       | +25℃  |      | 4    |       | ms     |

| Power Switch On-Resistance             | Ron                   |                                                                                    | Full  |      | 0.6  | 1     | Ω      |

| Peak Switch Current Limit              | I <sub>LIM_SW</sub>   |                                                                                    | +25°C | 0.9  | 1.3  | 1.65  | Α      |

| Switch Leakage Current                 |                       | V <sub>SW</sub> = 72V                                                              | +25°C |      | 0.01 | 1     | μΑ     |

| Mirror Voltage Drop                    | V <sub>MD</sub>       | $I_{APD} = 100 \mu A, V_{OUT} = 50 V$                                              | Full  | 2.90 | 3.05 | 3.21  | V      |

| Twinter veilage Brop                   | ▼ MD                  | $I_{APD} = 1mA, V_{OUT} = 50V$                                                     | Full  | 3.00 | 3.15 | 3.32  | V      |

| Current Monitoring                     |                       |                                                                                    |       |      |      |       |        |

| 1× Transfer Resistance                 | TR <sub>1×</sub>      | APD current to VMON transferring ratio, 1× gain                                    | Full  | 1.16 | 1.25 | 1.31  | kΩ     |

| 8× Transfer Resistance                 | TR <sub>8×</sub>      | APD current to VMON transferring ratio, 8× gain                                    | Full  | 9.50 | 10   | 10.52 | kΩ     |

| 1× Least End -0.5dB Gain Error Point   | lm <sub>1×</sub>      | Where the output is -0.5dB off the linear trendline                                | +25°C |      | 25   |       | μA     |

| 1× Most End 0.5dB Gain Error Point     | IM <sub>1×</sub>      | Where the output is 0.5dB off the linear trendline                                 | +25°C |      | 2.7  |       | mA     |

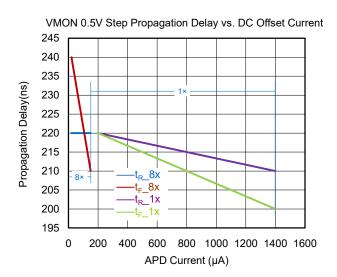

| Settle Time                            | t <sub>ST</sub>       | APD to VMON settle time, to 90% for rising and 10% for falling, to 1mA and to 10µA | +25°C |      | 250  |       | ns     |

| TH Effective Delay                     | t <sub>DELAY</sub>    | TH to track/hold and 1×/8× effective delay                                         | +25°C |      | 50   |       | ns     |

| Effective Hold Aperture Window         |                       | The time window for effectively holding                                            | +25°C |      | 3    |       | ns     |

| Holding Droop                          | $V_{DROOP}$           | Voltage droop measured in 10ms when holding 1V                                     | +25°C |      | 3    |       | V/s    |

| I <sub>LIM</sub> Programming Accuracy  | I <sub>LIM_APD</sub>  | Test with $R_{LIM} = 28k\Omega$ for $I_{LIM} = 2.4mA$                              | +25°C | 2    | 2.4  | 2.8   | mA     |

| VREF Pin                               | _                     |                                                                                    |       |      |      |       | •      |

| Reference Voltage                      | $V_{REF}$             |                                                                                    | Full  | 2.43 | 2.48 | 2.54  | V      |

| Load Regulation                        |                       | From 0 to 1mA                                                                      | Full  |      | 1.5  | 3     | %      |

| Temperature Co-efficiency              |                       |                                                                                    | +25°C |      | 32   |       | ppm/°C |

| Logic IO                               |                       |                                                                                    |       |      |      |       |        |

| Input Low Threshold                    | V <sub>IL</sub>       |                                                                                    | Full  |      |      | 0.4   | V      |

| Input High Threshold                   | V <sub>IH</sub>       |                                                                                    | Full  | 1.6  |      |       | V      |

| Input Low Souring                      | I <sub>LS</sub>       | Bias to V <sub>IL</sub>                                                            | Full  |      | 0.01 | 1     | μA     |

| Thermal Protection                     |                       |                                                                                    |       |      |      |       |        |

| Thermal Shutdown Temperature           |                       | Temperature rising                                                                 |       |      | 160  |       | °C     |

| Thermal Shutdown Hysteresis            |                       |                                                                                    |       |      | 15   |       | °C     |

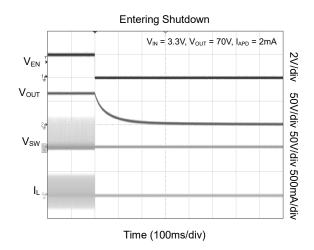

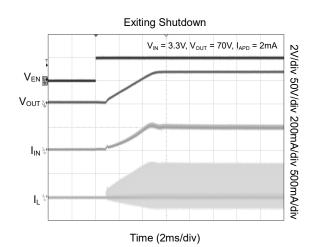

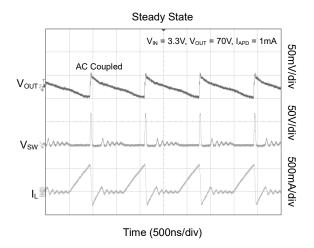

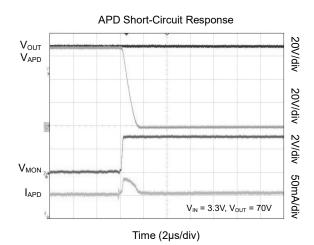

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = V_{EN} = 3.3V$ ,  $V_{OUT} = 70V$ ,  $T_J = +25$ °C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$V_{IN} = V_{EN} = 3.3V$ ,  $V_{OUT} = 70V$ ,  $T_J = +25$ °C, unless otherwise noted.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **DETAILED DESCRIPTION**

The SGM41282C is a non-synchronous Boost converter using the constant frequency peak current mode control scheme for high-output voltage application such as APD high voltage biasing.

The SGM41282C operates in discontinuous mode (DCM) to maintain the system stability for high conversion ratio for low input voltage to high output voltage. For DCM, it can eliminate the effect of right-hand zero of Boost converter. Inductor current rises from zero each cycle, there is no accumulation of inductor current when duty cycle is higher than 50%, so it can simplify the need for compensation circuit.

The SGM41282C integrates APD biasing current mirror and trans-impedance amplifier (TIA) function. The TIA converts the mirror current to voltage signal and sends to VMON pin. 1× or 8× current mirror gain can be set by GAIN pin. Track and hold function can be set by XOR logic of THXOR and TH pin.

#### **Enable and Disable**

When the EN pin is pulled to high voltage, the SGM41282C is enabled. When the EN pin is pulled to low voltage, the SGM41282C goes into shutdown mode. Less than  $1\mu A$  input current is consumed in shutdown mode.

#### APPLICATION INFORMATION

#### **Extending the Monitoring Range**

The GAIN pin input is for selecting 1×/8× gains for proper output levels, extending the appreciated monitoring range by 8 times. The gain could be changed during tracking or holding, with less interference injection. As the fiber receiver monitors signal in very high dynamic range but less resolution, this circuit brings out a unique tradeoff between the resolution and dynamic range.

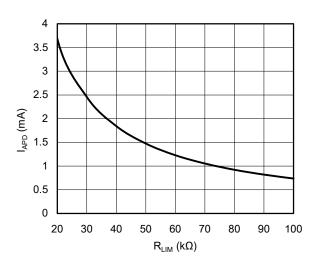

#### **Programming the Current Limit Level**

Connect a resistor from RLIM pin to AGND to program the current-limit threshold. The  $R_{\text{LIM}}$  for setting the current limit level is calculated with the following equation, and please refer to the Figure 3 for the typical  $I_{\text{LIM}}$  to  $R_{\text{LIM}}$  plot.

$$R_{LIM}(k\Omega) = \frac{70}{I_{APD-MAX}} (mA)$$

Figure 3. APD Current Limit vs. R<sub>LIM</sub>

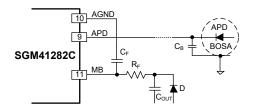

#### Ripple Filtering

A simple RC filtering circuit could help in suppression of ripple applied at MB input, which then improving the modulation effect to the signal picked-up in the optical channel, which helps in getting better eye diagram opening. Refer to the Figure 4, the resistance of the R inserts drop to be compensated.

Figure 4. An RC Filtering for Ripple Suppression

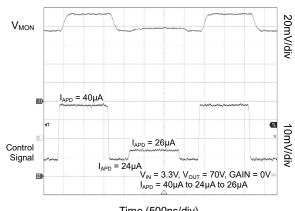

#### **Burst Pulse Response**

The Figure 5 shows the capture of waveform at the VMON pin in tracking mode, where a train of current pulses with two different peak values is applied to the APD output, representing the case of burst pulse receiving.

Time (500ns/div)

Figure 5. Burst Pulse Receiving Waveform

#### **Backward Scattering**

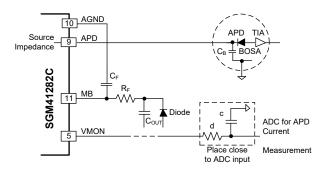

Careful layout of the circuit optimization is desired for assuring fast transient measurement to APD current. Illustrative circuit is showed in the Figure 6, which shows necessary layout considerations. The  $C_{\rm B}$  is low loss capacitor installed in the TO-can in a BOSA, which holds the potential applied on the APD, and the  $C_{\rm B}$  should be evaluated on the final PCB, or , it will slow down the settling time of the monitoring output at the VMON besides the intrinsic propagation and settling of the SGM41282C.

## **APPLICATION INFORMATION (continued)**

The d and the c placed close to the ADC input are for ringing dump, which occurs when the ADC input switch cuts for holding. These two components do not affect the transient, but induce interference to the measurement. Those components should also be evaluated on the final PCB. The recommended values of d and c are  $10k\Omega$  and 22pF.

Figure 6. Illustration Circuit

#### **External Components Selection**

As the Boost circuit works at about 850kHz, capacitors with good high frequency performance are needed for the application circuit. As the storage capacitor (the  $C_{OUT}$  in the Figure 1 or the Figure 2) works under high bias voltage, please refer to the capacitor's datasheet to assure its effective capacitance is more than  $0.1\mu F$  at the output voltage.

**Table 1. Key Components Selection Reference**

| L<br>(µH) | Diode<br>(Schottky Small<br>Signal) | С <sub>оит</sub><br>(µF 100V) | C <sub>IN</sub><br>(µF) | R <sub>F</sub><br>(Ω) | C <sub>F</sub><br>(μF 100V) | C <sub>REF</sub><br>(nF) |

|-----------|-------------------------------------|-------------------------------|-------------------------|-----------------------|-----------------------------|--------------------------|

| 4.7       | BAT46W                              | 0.1                           | 10                      | 100                   | 0.1                         | 470                      |

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| JULY 2024 – REV.A.2 to REV.A.3                            | Page |

|-----------------------------------------------------------|------|

| Added Package Thermal Resistance section                  | 2    |

| Updated Package Outline Dimensions                        | 10   |

| FEBRUARY 2024 – REV.A.1 to REV.A.2                        | Page |

| Updated Pin Description and Detailed Description sections | 3, 7 |

| NOVEMBER 2020 – REV.A to REV.A.1                          | Page |

| Updated Marking Information section                       | 2    |

| Changes from Original (DECEMBER 2019) to REV.A            | Page |

| Changed from product preview to production data           | All  |

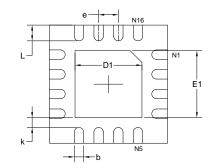

## PACKAGE OUTLINE DIMENSIONS TQFN-3×3-16L

**TOP VIEW**

**BOTTOM VIEW**

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | _         | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|-----------|------------------|-------------------------|-------|--|

|        | MIN       | MIN MAX          |                         | MAX   |  |

| A      | 0.700     | 0.800            | 0.028                   | 0.031 |  |

| A1     | 0.000     | 0.050            | 0.000                   | 0.002 |  |

| A2     | 0.203     | REF              | 0.008                   | REF   |  |

| D      | 2.900     | 3.100            | 0.114                   | 0.122 |  |

| D1     | 1.600     | 1.800            | 0.063                   | 0.071 |  |

| Е      | 2.900     | 3.100            | 0.114                   | 0.122 |  |

| E1     | 1.600     | 1.800            | 0.063                   | 0.071 |  |

| k      | 0.200     | MIN              | 0.008                   | 3 MIN |  |

| b      | 0.180     | 0.300            | 0.007                   | 0.012 |  |

| е      | 0.500 TYP |                  | 0.020                   | TYP   |  |

| L      | 0.300     | 0.500            | 0.012                   | 0.020 |  |

| eee    | 0.0       | 080              | 0.0                     | 003   |  |

NOTE: This drawing is subject to change without notice.

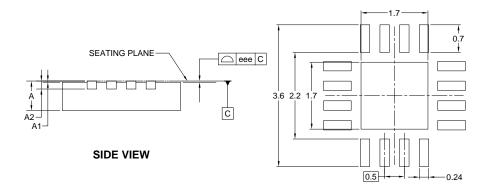

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-3×3-16L | 13"              | 12.4                     | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13"       | 386            | 280           | 370            | 5            |